Q431. Explain the concept of a lockup latch?

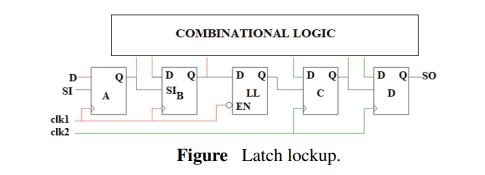

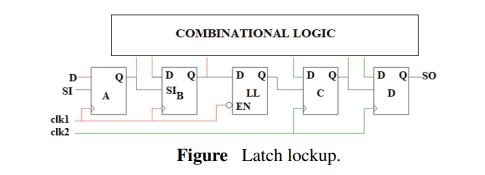

The latch lockup is the concept in STA where a higher clock skew is present.

The lockup latch is just like a transparent latch, which is placed at that point,

where clock skew is maximum. To reduce the clock skew and follow the hold

time constraints, the lockup latch is used, during design for testability. The

Figure shows the concept of lockup latch.

The clock skew occurs mostly in the systems where multiple clocks are

used. The clock skew can occur during shift and capture time. The clock skew

can be minimized during a shift by grouping all the flip-flops which are run by

the same clock. To remove clock skew completely, the lockup latch should be

inserted where the domains cross. This will solve the problem of clock skew

during shift.

In scan-chain, the lockup latch will act as an end-point. The scan chain

can be reordered, by grouping the cells from starting to lockup latch as one

domain, and from lockup, latch to the last cell as a second domain. That way

makes the clock grouping preserved.

The timing path will be divided as:

Domain 1: Launch flip-flop to lockup latch

Domain 2: Lockup latch to capture flip-flop

The lockup latch can be placed in between cells automatically or by using

a scan chain order file.

There may be multiple clock paths between clock domains that are

available during capture. The clock skew during capture can be reduced by a

pulse one clock per pattern.

Q432. If the clock skew is large, can you use buffers to avoid hold time constraints violation?

It is discouraged practice to use the buffers when clock skew is large. As the number of buffers will be increased, which will automatically degrade the performance of the circuit as area and power factor will also be enhanced. It will increase the chances of on-chip variation (OCV). The optimized solution for handling large clock skew and hold time constraints is the insertion of a lockup latch.

Q433. What are the advantages of a lockup latch?

- It is power and area efficient.

- The device can handle more OCV (on-chip variation) easily.

- This is the robust method to deal with hold time constraints during scan shift mode.

- It prevents data corruption i.e. data overridden which occurs due to clock skew.

Q434. Is there any difference between the lockup latch and lockup register?

As the lockup latch occupies approximately half of the area than the lockup register, so lockup latch is having an optimized solution in terms of power and area as compared to the lockup register. During negative lockup latch, there is no need to worry about timing constraints at functional frequency. But this is not for the lockup register. So, the lockup latch is more prevalent than lockup register, during the design process and timing analysis.

Q435. What do you understand by the term ‘clock latency’?

When there is a difference between the arrival of the clock from source to pin. It is further divided into source latency and network latency. Network latency measures how fast the network is running and source latency specifies the propagation delay from the source of the clock to clock port.

Q.436. Is the term clock skew and global skew the same?

No, the clock skew and global skew both are different in terms of connections. The global skew is related to skew in between two mutually exclusive flipflops, i.e. which are not related by fan-in or fan-out. The skew between two independent flip-flops is known as global skew, whereas the skew in between two dependent flip-flops are known as clock skew.

Q.437. Can you fix the timing path? If yes, then give at least three ways to fix the timing path?

Yes, timing paths can be fixed. It can be done by any of the following ways:

- Logic optimization

- Use of macros

- Placement of logic/capture/launch flip-flop

- Pipeline can be enhanced

- Replicate drivers and split number of receiving gates

- Divide large serial operation into multiple smaller length parallel operations.

- Switch to the cells having low threshold voltage, high gate leakage, and fast speed.

- Use one hot encoding register, that will increase the speed of operation.

- Use power trade-off techniques.

- Physical design techniques to reduce capacitance and speed up the wire delays.

Q.438. What is a false path in static timing analysis?

The false path refers to a path that is not required to be optimized during timing analysis. It means it is not necessary to complete the capture and launch a task in the same clock cycle. It is known as a false path. It is not optimized by the timing optimization tool.

Q.439. What is one hot encoding method?

In the one-hot encoding technique, the number of flip-flops is increased and combinational logic is minimized. It is a state assignment method in a finite state machine. It assigns one flip-flop to each state of FSM. The number of interconnections between logic gates is reduced, which further reduces the propagation delay and speed up the finite state machine.

Q.440. . What is the concept of a multicycle path?

Usually, the data setup and hold operation are done during a single clock pulse. But there are some cases where launch and capture can take more than one clock cycle i.e. combinational delay between launch and capture edge is more than one cycle. This is known as a multicycle and timing path through this combinational logic is known as the multicycle path. Although the data is captured during the same clock cycle, in the case of the multicycle path, the capture edge of flip-flop becomes active after a specific number of cycles. Similarly, the designer will take care of the fact that data will be launched not after every single clock cycle. In such cases, the timing tool will be provided by exception or overridden flag so that it can postpone the launch and capture check after one clock cycle.