Pessimism and Optimism in Timing Analysis

"Too much optimism or too much pessimism can negatively impact one's progress. There should always be a balance."

The above line holds equally true even in the world of VLSI industry.😂 A little pessimism is not dangerous but is helpful in meeting the timing of a design. The closest example I can come up with to explain this scenario is that If someone is able to succeed when the circumstances are slightly against him, he will definitely perform well when the circumstances are in favor. A slightly pessimistic constraints are provided to the tool so that we don't get to see any surprises in silicon. But remember that anything in excess is bad. Any extra pessimism in the timing analysis increases the effort of tool to fix the critical timing paths and can negatively impact the other parameters like power and area. On the other hand, optimism in timing analysis might result in the silicon failure. It is therefore necessary to remove extra pessimism and optimism from timing analysis.

Need of adding pessimism:

Simple explanation is that perfection can't be achieved in the practical scenario.😎 Same cells present at the different parts of the chip can have different delay values under the same operating condition. The fabrication process is not an ideal process and due to non ideal nature, the same cell at different parts of the chip will have a variation in its structure which results in the different delay numbers. Other than fabrication process, other reason for adding pessimism in the design is due to the difference in the temperature at different parts of chip due to formation of hotspots. To take this into account beforehand in EDA tools itself, OCV is considered and derates are applied to the design.

How pessimism is added to the design?

Timing engineers add pessimism to the design with the help of derates. Derates are applied on the launch clock path and capture clock path. Derate value is decided based on the guidelines and suggestions of the library vendor according to the previous fabrication experience and PVT conditions. With the refinement of the fabrication process, the value of derates becomes less pessimistic.

Setup analysis (Late analysis):

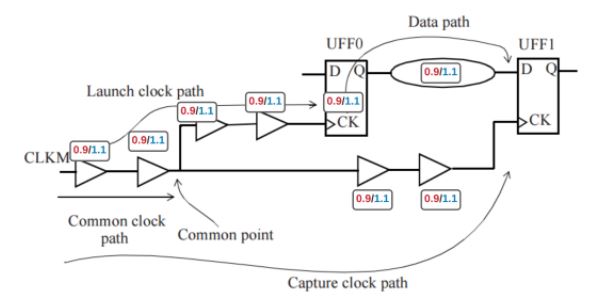

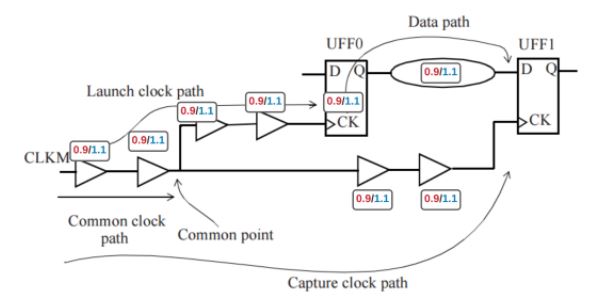

Consider a Register to Register timing path as shown in the figure below. Let's say all the cells shown below have a delay of 1ns. Now, to model On-chip variation, 10% of derate is applied. Due to the derate application the best delay value of the cell is 0.9ns and worst delay value is 1.1ns. Let's consider Tclk as 3.5ns and Tsetup = 0.6ns

To make condition more pessimistic for setup analysis, launch path is delayed (worst delay value) and the capture path is advanced (best delay value).

Worst scenario for setup analysis:

Launch path delay: 1.1 + 1.1 + 1.1 + 1.1 + 1.1 + 1.1 = 6.6ns

Capture path delay: 0.9 + 0.9 + 0.9 + 0.9 + 3.5 - 0.6 = 6.5ns

Setup slack = 6.5-6.6 = -0.1ns (Setup Violation)

But if you notice the two common buffers present in the clock path have different delay values in launch clock path (1.1) and capture clock path (0.9). How can a same cell have two different delay values at the same time. Taking two delay values for the same cell adds extra pessimism to the design which needs to be adjusted. The adjusted value is called as CPPR value.

CPPR = (1.1+1.1) - (0.9+0.9) = 0.4ns

Setup analysis with CPPR adjustment:

Consider one value for the common cells in the common path, say, 1.1ns. The revised equations would be

Launch path delay: 1.1 + 1.1 + 1.1 + 1.1 + 1.1 + 1.1 = 6.6ns

Capture path delay: 1.1 + 1.1 + 0.9 + 0.9 + 3.5 - 0.6 = 6.9ns

Slack = +0.3 (MET)

The setup slack in without CPPR adjustment was -0.1ns but after doing the CPPR adjustment the setup slack value is +0.4ns. There was an extra undue pessimism added in the first case which was removed in the second case. As you can see that the slack value is -ve in the first case with extra pessimism and is +ve when the extra pessimism is removed. If the extra pessimism would not have adjusted, the path would have violated and the tool would have needed more time to fix this path, unnecessarily.